(文章来源:电子工程专辑)

合见工软Fellow、研发副总裁吴秋阳先生日前在2022国际集成电路展览会暨研讨会(IIC)上发表题为“解码高端芯片,加速数字经济”的主旨演讲时,重点分析了国内外EDA行业的发展现状、产业环境、机遇和挑战,并详细介绍了合见工软如何通过打造数字验证全流程和系统级电子设计EDA解决方案,助力中国芯片产业实现突破式发展。

合见工软Fellow、研发副总裁吴秋阳

合见工软Fellow、研发副总裁吴秋阳

EDA的发展现状与产业环境

吴秋阳首先回顾了EDA行业的四个发展阶段:

第一阶段是EDA诞生之前,从电子管到晶体管,电路设计从手工绘制发展到计算机辅助。

第二阶段是可编程逻辑器件开始成熟,这一阶段的标志是1980年发表的《超大规模集成电路系统导论》,它提出用可编程的硬件语言(HDL)来实现电路编程,对电路进行自动综合和模拟,以及设计流程的自动化。在这个过程中,我们也对设计流程进行了很多的抽象,形成了很多点工具,对痛点和难点进行自动化和算法化。这个阶段的特点是,除了三大国际EDA公司之外,很多其他公司能够提供局部最优解,这些局部最优解往往和全局最优解吻合度较高,所以点工具是可以生存的。

第三阶段是到2000年之后,由于制程进一步演进,如果只在前端进行逻辑设计,不考虑后端制造工艺要求就会形成设计无法收敛,所以就促成了全流程的集成,算法也变得具有前瞻性,比如逻辑综合的时候就要考虑布局布线的影响,更进一步在设计过程中考虑制造工艺的可能性。由于技术上的底层逻辑,基本上形成了以美国Synopsys、Cadence两大公司为主建立的完整的准封闭式平台的现状;还有两家公司SiemensEDA和Ansys也有自己的拳头产品,从而在产业链中有立足之地。

第四阶段是2015年之后,EDA行业进入探索与突破阶段。大数据、云计算、机器学习、人工智能、开源EDA、硅编译器、异构芯片、3D等技术在上下游扩展,对EDA提出了更高的新发展要求。市场形成了Synopsys、Cadence、SiemensEDA三大EDA巨头。这个阶段有不少新的概念和方向,有些昙花一现并没有落地结果,但有一些做出了不错的成绩。

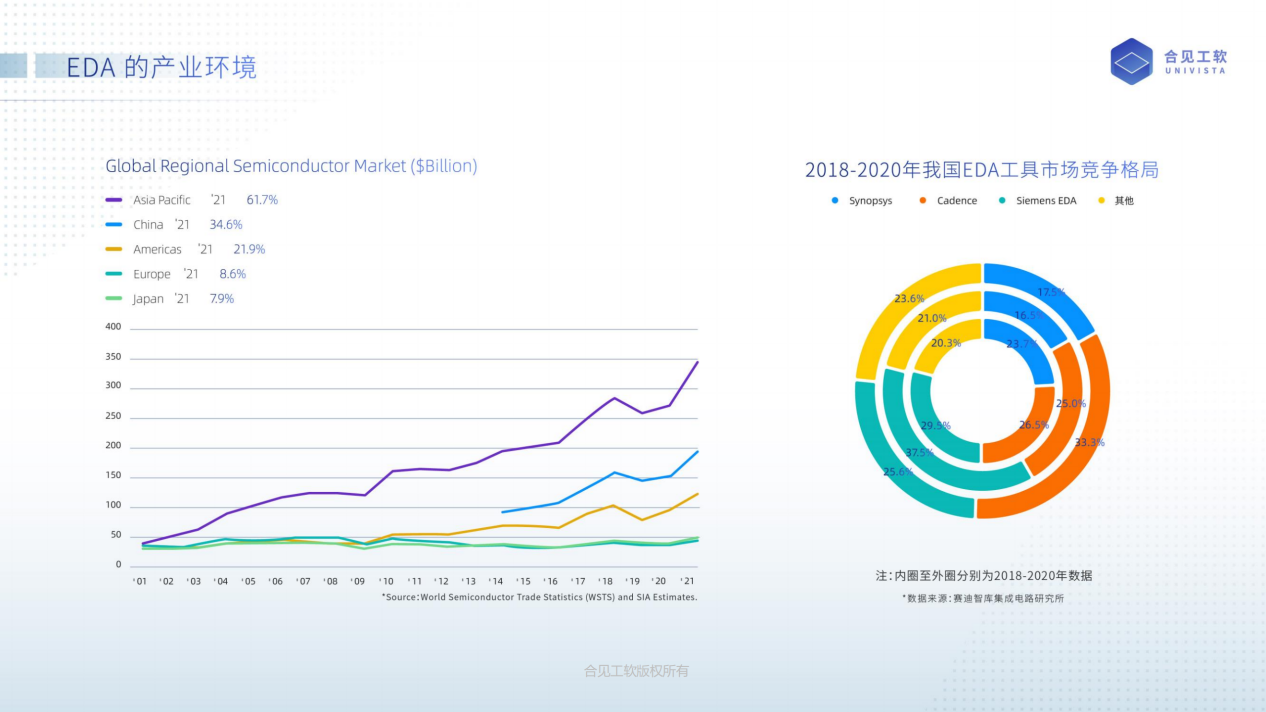

EDA面向的是全球半导体市场,中国进口芯片中只有35%用在国内设备上,但却消耗了全球芯片总量的77%以上。然而,国内市场能够用于芯片设计的EDA工具并不是特别多,三大国际EDA公司长期垄断约80%市场份额,国产EDA市场份额大约只有10-12%。

发展高性能芯片的机遇和挑战

“我们的客户都是针对高端芯片,那么高端芯片的需求在哪里呢?”吴秋阳分析称,EDA支撑起了5000亿美元规模的半导体行业,以及数十万亿美元规模的数字经济。到2025年,中国希望将数字经济核心产业增加值占国内生产总值的比重提高到10%。“这是一个了不起的愿景,需要我们在包括云计算、人工智能、大数据、自动驾驶、5G通信和工业物联网在内的各个领域全面发力。”

在他看来,无论是提供产品还是提供服务,其差异化往往都是从最底层的硬件开始。

首先,由于疫情和国际政治问题,为了确保供应链的自主可控和安全可靠,各个系统厂商都希望能够控制自己芯片的设计制造。

其次,“合久必分”。一直以来,能够提供算力和通信的都是CPU/GPU这样的通用型标准芯片,但缺点是无法在细分场景下实现最佳优化。为了让自己的产品或者服务具备差异化竞争优势,不少系统厂商纷纷开始涉足芯片行业,有的甚至会针对不同场景设计不同的芯片,例如亚马逊面向计算密集、I/O密集和机器学习加速就设计了三款不同的芯片,这些对EDA企业而言都是很好的机会。

最后,全球气候变暖,低功耗高能效的产品也是人类文明的发展方向。高科技公司也需要设计自己独有的高能效、低能耗、高性能产品,这也带来了很多机会和挑战。

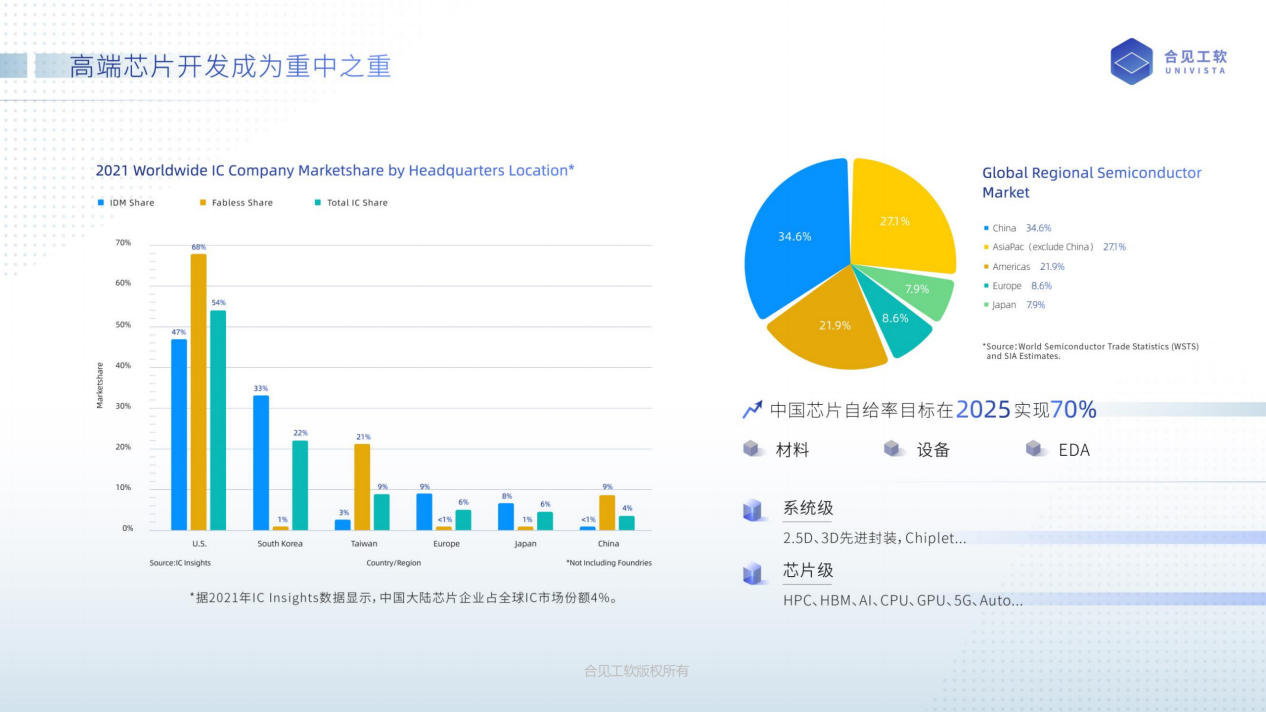

“中国芯片自给率的目标是在2025年实现70%,但中国IC芯片目前在国际市场的份额只有4%,差距非常大,要实现70%的芯片自给率还需要很大的投入和努力。”吴秋阳援引分析机构的数据称,用于半导体制造的材料、设备和EDA,将是实现该目标的三大支柱。其中,涉及EDA的有两个方向:一是涵盖高性能计算、人工智能、通用CPU、GPU等应用的芯片级EDA,二是用于2.5D、3D先进封装、Chiplet等领域的系统级EDA。

他指出,规模、复杂度、市场与生态是高性能芯片发展道路上面临的主要挑战:从规模来讲,芯片越来越大,复杂度也大幅提升,不仅需要通过工艺,还需要通过先进的封装技术来实现,在软件层次与多源多版本方面也需要持续增加IP的集成;在市场与生态方面,越来越短的窗口期等各种因素给高性能芯片发展带来了很大的挑战。

从最难的验证市场开始

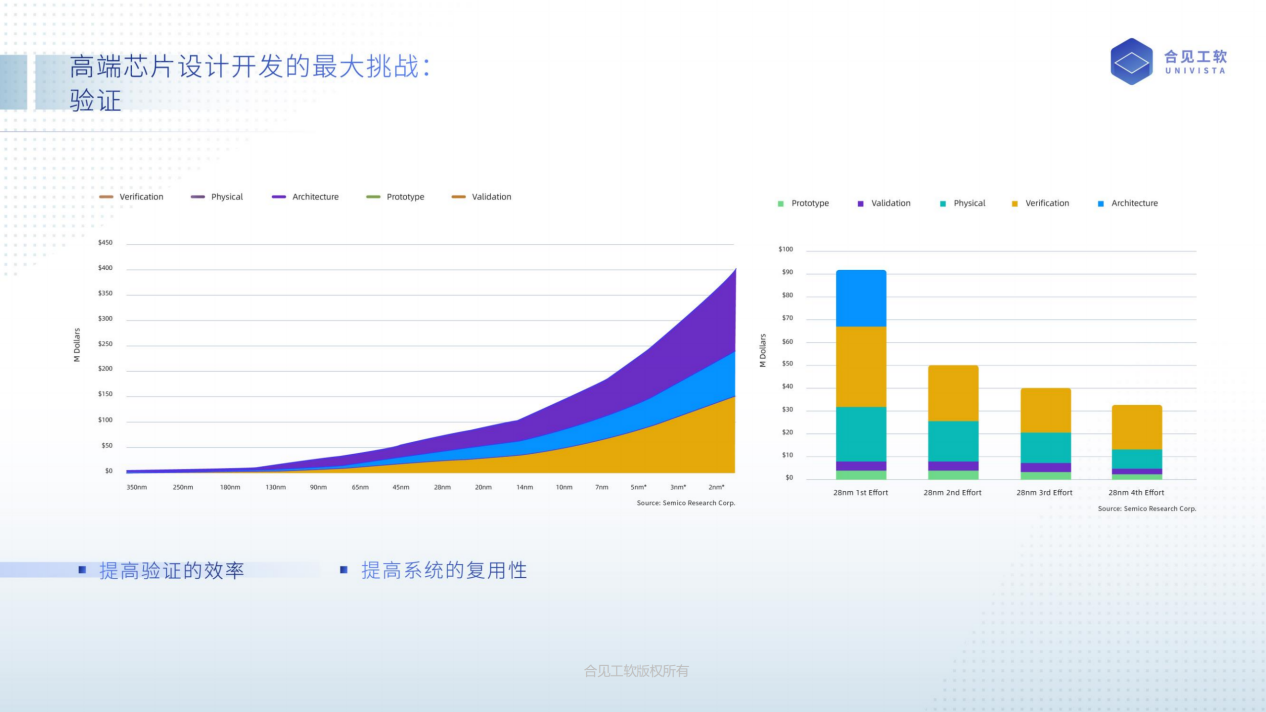

之所以选择最难的验证市场,吴秋阳解释说,当前解决高端芯片设计开发的最大挑战就是来自验证阶段。从下图可以看到,随着制程工艺的不断演进,验证成本增加得很快,最先进芯片开发成本的30%以上来自验证阶段。以高通今年发布的自动驾驶芯片为例,它需要验证效率的提升、验证的可预期性、验证的质量保证、以及验证的多样化需求。

合见工软销售副总裁刘海燕随后在接受AspenCore独家专访时也表达了同样的观点。她表示,在EDA领域的众多细分方向中,验证伴随着芯片设计的全过程,随着工艺的演进和设计的复杂化,验证工具的开发存在较高的技术壁垒和准入门槛,目前已经成为研发工具成本占比最高的一部分,因此验证领域的突破对中国芯片产业发展至关重要。

为了应对高端芯片在验证方面的种种挑战,合见工软提出基于验证任务驱动的全场景数字验证系统,从软硬件核心验证引擎出发,到验证管理与调试定位,以及完善的验证解决方案。合见工软已经推出了多款EDA产品和解决方案,包括数字仿真器UVS、FPGA原型验证系统UVAPS、仿真调试工具UVD、验证效率提升平台VPS、系统级IP验证方案HIPK等,以更好地解决芯片开发中的功能验证、调试和大规模测试管理等不同任务的挑战。

此外,随着制程工艺的不断演进,摩尔定律效应日渐趋缓,2纳米或者1纳米时会表现得更加明显,所以先进封装会是未来的方向,特别是Chiplet已成为芯片设计业的主流技术趋势之一,随之带来了设计规模、设计工具、设计检查等方面的挑战。这就需要打破IC、Interposer、Package、PCB设计协同的壁垒,建立系统级一体化设计和检查环境。

为此,合见工软在先进封装设计、板级设计领域进行了相应的布局。合见工软于今年6月推出了先进封装协同设计检查工具UVI的Sign-off级完整功能版,可在同一设计环境中导入多种格式的IC、Interposer、Package和PCB数据,支持全面的系统互连一致性检查;此外合见工软也在着力开发PCB和封装设计EDA产品方案。

了解更多,请查看原文:合见工软:解码高端芯片,加速数字经济-icspec