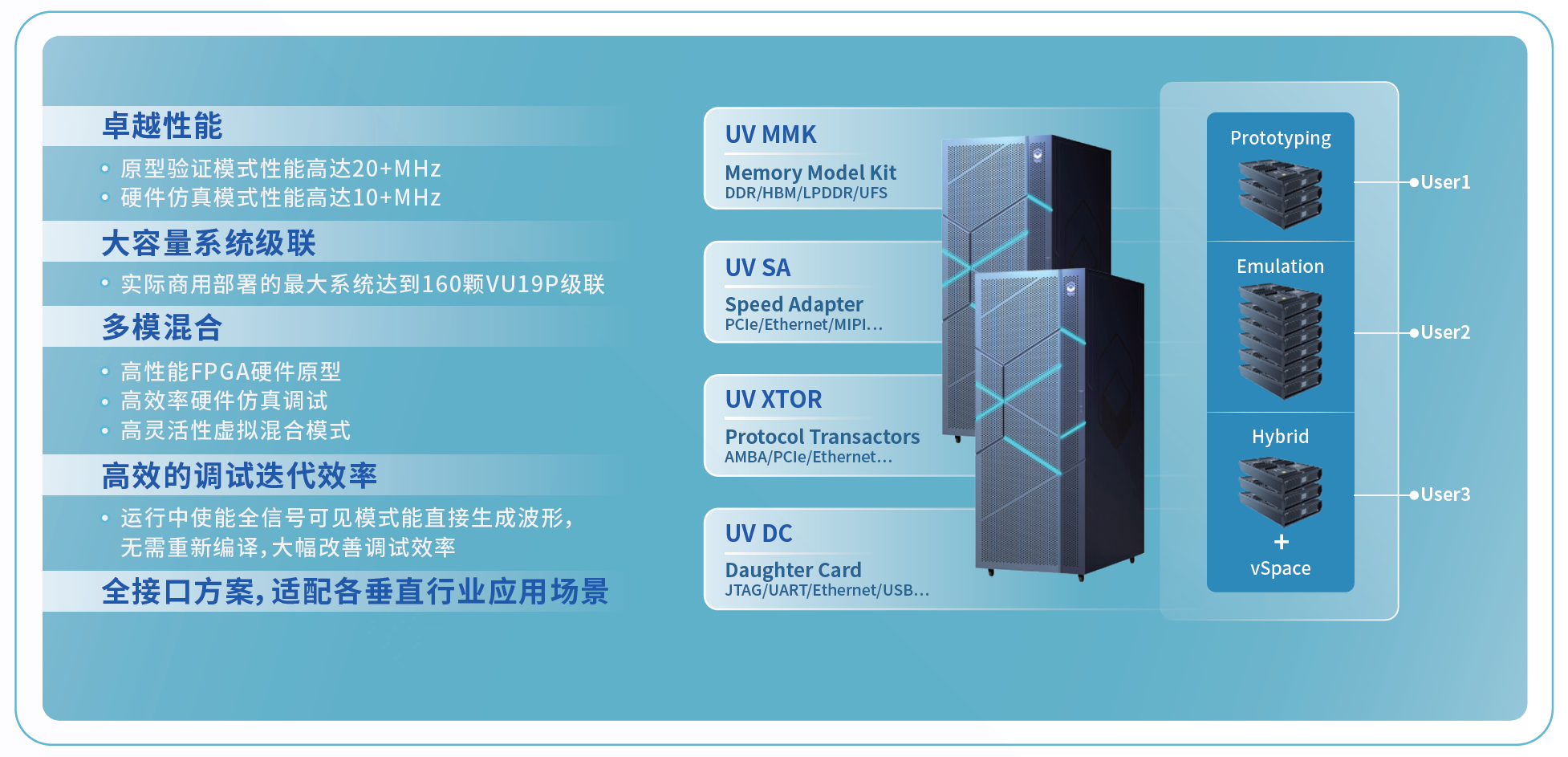

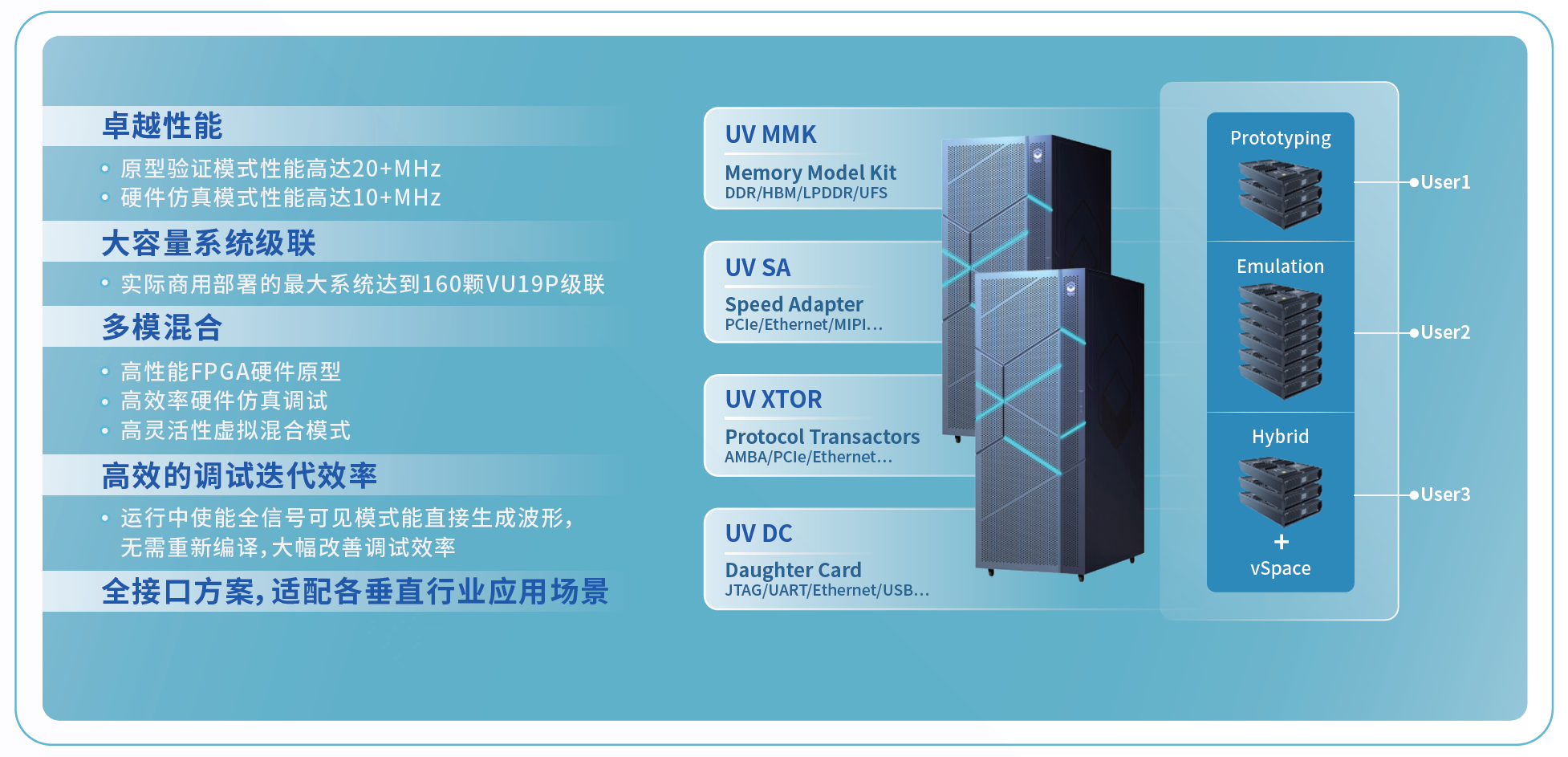

合见工软商用级全场景验证硬件系统UniVista Unified Verification Hardware System(简称“UVHS”)适用于大规模ASIC/SOC 软硬件验证的各种应用场景,可广泛用于智能驾驶、数据中心、人工智能、5G通信和智能手机等各类高端芯片的开发,为芯片开发者提供了高效的软硬件验证方式,大幅缩短验证周期,加速芯片上市。

UVHS目前已经在客户处实际商用部署的最大系统达到160颗VU19P级联,超过60亿逻辑门,得益于核心技术全局时序驱动的自动分割引擎,在超大型系统场景下仍能保持10+MHz的高运行性能。UVHS也提供充足可配置的互联通道,支撑灵活的系统扩展需求。

UVHS的领先技术:

- 业界领先的性能:原型验证模式性能高达20+MHz,硬件仿真模式性能高达10+MHz

- 智能的集成编译软件UVHS Compiler内置先进的时序分析引擎,作为合见工软核心自主自研技术,可很大程度获取验证专用FPGA阵列硬件系统的峰值性能

- 稳定可靠的大容量级联系统:已实际商业化部署、稳定运行的级联系统所支持的单一设计规模轻松突破60亿门

- 高效的一体化解决方案:集成自主研发的UVHS Compiler和Runtime软件,帮助用户快速定位调试,优化用户设计输入、约束和流程,加速RTL to running system的迭代能力,相对于传统方案,能缩短设计启动时间40%~60%

- 增强的调试迭代效率:运行过程使能全信号可见模式能够直接生成波形,无需重新编译,大幅改善调试效率

- 支持UPF低功耗设计

- 支持基于DPI-C的 System C testbench

- 支持和虚拟平台进行混合仿真验证:更早开始进行软件开发和软硬件架构探索,实现左移

- 丰富的接口子卡、高速接口速率适配器、虚拟接口模型和存储模型,如PCIe Gen5,Ethernet,MIPI,DDR5,HBM3等等,适配各种使用模式下的接口验证需求